据外媒及芯片行业3日消息,台积电3纳米制程良率超过预期水平,或在75%至80%之间。台积电董事长刘德音当天在典礼中表示,目前台积电3纳米制程良率已与5纳米量产同期相当,进入大量生产。

芯片良率反映晶圆上合格芯片数量与芯片总数的比值,数值越大说明有用芯片数量越多,浪费越少,成本越低,利润越高。芯片行业认为,三星电子和台积电谁先实现“黄金良率”90%的突破,将在此轮竞争中取胜。有观点指出,在实际产品出厂之前,无法确定台积电实际制程良率。但考虑到台积电在5纳米、4纳米制程良率提升上的速度快于三星电子,后者能否延续先发量产后的优势有待观望。

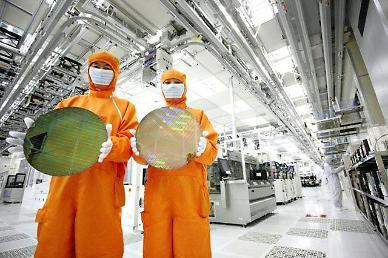

上月29日,台积电董事长刘德音在南部科学园区晶圆18厂新建基地举办3纳米量产暨扩厂典礼。【图片提供 韩联社】

去年6月30日,三星电子宣告基于全环绕栅极(GAA)架构的3纳米开始量产首批芯片,成为全球首家量产3纳米芯片的芯片代工厂。不同于此前使用的鳍式场效应晶体管(FinFET)架构,GAA架构将减少电耗、提升性能,在技术层面意义重大。三星电子自2000年代初期启动GAA技术研究,2017年将其用于3纳米制程。台积电则延续FinFET架构,最快2纳米才评估导入GAA架构。

但在良率方面,此前有台媒报道称,三星电子3纳米良率仅20%,企业与美国公司Silicon Frontline Technology扩大合作以提高良率。三星电子随后对其进行了否认,但未对外公开具体良率信息。目前韩国行业方面预测其3纳米良率大约在60%左右。

在订单方面,更高的良率成为高通等代工厂客户选择的关键,但后者也不得不考虑价格方面的问题。去年主要客户之一的苹果曾对台积电的2023年涨价要求提出拒绝。据台媒报道,1月起台积电大多数制程的代工价格将上涨约6%。目前台积电将3纳米制程的12英寸晶圆代工单价定在2万美元,较此前的5纳米制程晶圆(1.6万美元)提高25%。

专家指出,在3纳米芯片竞争中,三星电子可能凭借GAA架构在速度和电力消耗量方面的优势吸引更多客户订单,但能否及时供货及提升良率成为制胜关键。

三星电子高管展示3纳米芯片。【图片来源 三星电子】